USRP enables engineers to quickly design and build a powerful, flexible, and independent software radio system. Configured with different RF boards, it can meet the needs of different software radio applications: from DC to 6 Ghz.

USRP UN200/UN210

USRP enables engineers to quickly design and build a powerful, flexible, and independent software radio system. Configured with different RF boards, it can meet the needs of different software radio applications: from DC to 6 Ghz. Building on the success of USRP2, the HM USRP N200 series offers higher quality performance and greater flexibility. The series includes the USRP N210 for custom needs and the USRP N200 for low cost solutions.

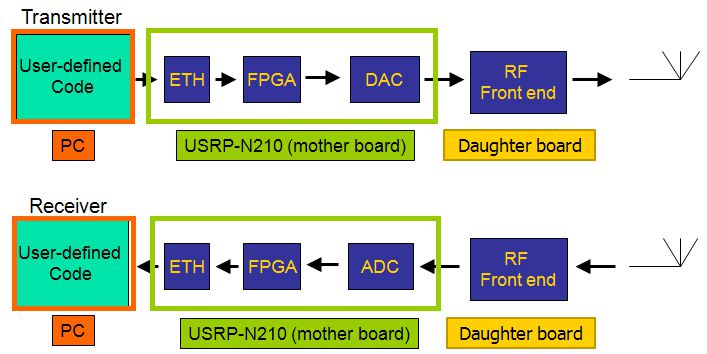

High-speed and high-precision ADCs and Dacs enable the system to process signals with a wider bandwidth and higher dynamic range. Gigabit Ethernet interfaces enable wireless systems built by the USRP to simultaneously transmit and receive RF signals with up to 50 MHz bandwidth. The HM USRP N200 series is built on Xilinx® Spartan® 3A-DSP FPGAs, which are suitable for DSP applications and enable composite signals to be sampled at high speeds. The USRP N210 is based on a powerful FPGA, almost 150% of the USRP N200, to cater to specific needs.

The processing of high sampling rates for both models, such as digital up and down conversion, is done in the FPGA. Low sampling rate operations can be done in the host or in an FPGA containing a 32-bit RISC processor. The USRP's configuration and firmware are stored in flash memory on the board, making it easy to program over Ethernet.

Two-channel on-board digital down-conversion (DDC) mixing, filtering, and extraction (starting at 100 MS/s) of the signal converging on the FPGA. Two digital up-conversion interpolations before converting it to the frequency to be output make the baseband signal at 100 MS/s. The combination of DDC and DUC with high sampling rates also greatly simplifies the requirements for analog filtering.

Multiple USRP can be linked together to form a fully coherent multi-antenna system for MIMO mode. The master oscillator can be locked to an external reference clock, for which the 1PPS input is designed to cater for high-precision applications. There is also an optional GPSDO inside. The accompanying daughter board provides a flexible, seamless RF front-end device. Rich, selectable daughter boards provide a DC to 6 GHz selection range.

● Two 100 MS/s 14-bit analog-to-digital conversion

● Two channels 400 MS/s 16-bit digital-to-analog conversion

● Digital downconversion with programmable extraction rate

● Digital up-conversion with programmable interpolation rate

● Gigabit Ethernet interface

● 2 Gbps high-speed serial port for expansion

● Can handle bandwidth up to 100 MHz

● Capable of streaming signals up to 50 MHz wide

● The module structure supports a wide variety of child boards

● Auxiliary digital-analog I/O interfaces support complex RF controls such as RSSI and AGC

● Fully coherent multi-channel system (MIMO capable)

● 1 MB of on-board high-speed SRAM

● TCXO reference frequency

● Includes an optional GPS locked reference oscillator

The entire USRPN200 series design is open source, including schematics, firmware, drivers, and even is FPGA and daughter board design. When combined with open source GNU software Radio, you get a fully open software radio system that makes it possible to build a commodity on a host signal processing platform. It provides a complete development environment to create your own software radio platform. While most are in software development environments with the GNUradio community, this HM USRP N200 series is flexible enough to accommodate other options. Some users have created their own development environments for USRP, such as the USRP environment that is currently integrated into LabVIEW and MATLAB/ Simulink.

Universal Hardware Driver (UHD) provides support for USRP hardware, which works on all major platforms (Linux, Windows, and Mac); It can be built with GCC, Clang, and MSVC compilers, providing cross-platform development possibilities, and UHD's purpose is to provide host drivers and apis for USRP products. This allows users to use the UHD driver independently or flexibly with third-party applications such as Gnuradio, Labview, or Simulink

Input:

2 input channels or 1 pair of I-Q

Sample rate: 100 MS/ s

Resolution: 14 bits

Spury-free dynamic range (SFDR) : 88 dB

Output:

2 output channels or 1 pair of I-Q

Sample rate: 100 MS/ s

Resolution: 16 bits

Spury-free dynamic range (SFDR) : 80 + dB

Clock and synchronization:

PPS Input: 3 to 5 V DC power

Reference clock: 5 or 10 MHz

Connector type: SMA

MIMO extension port

Auxiliary I/O:

High-speed digital I/O: 32-bit

Analog input: 4 channels

Analog output: 4 channels

FPGA

USRP N200: Xilinx® Spartan3A-DSP1800

USRP N210: Xilinx® Spartan3A-DSP3400

bandwidth

50 MHz instantaneous bandwidth (8-bit mode)

Instantaneous bandwidth of 25 MHz (16-bit mode)

Full duplex

Power requirements:

6VDC, 3A

(including requirements for child boards)

Supported operating systems

•Linux

•Mac OS X

•Windows